SiC的晶体缺陷

时间:2025-01-11 发布人:admin 点击数:0

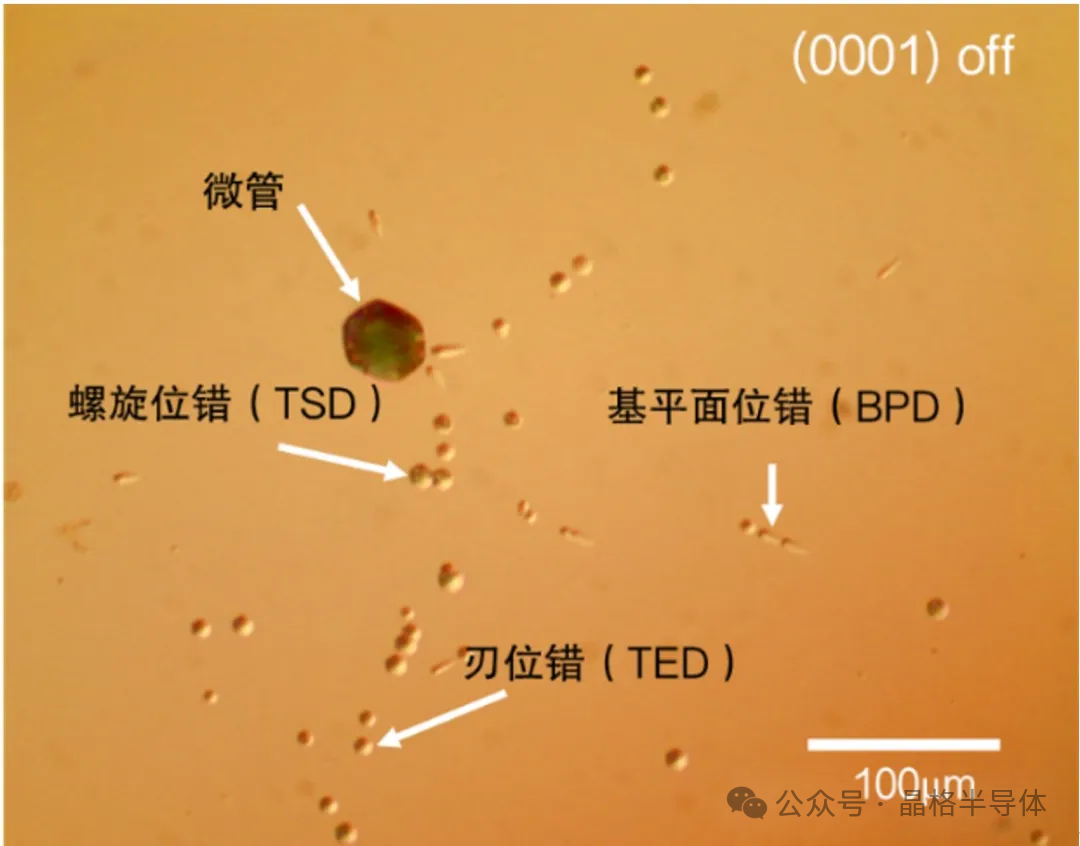

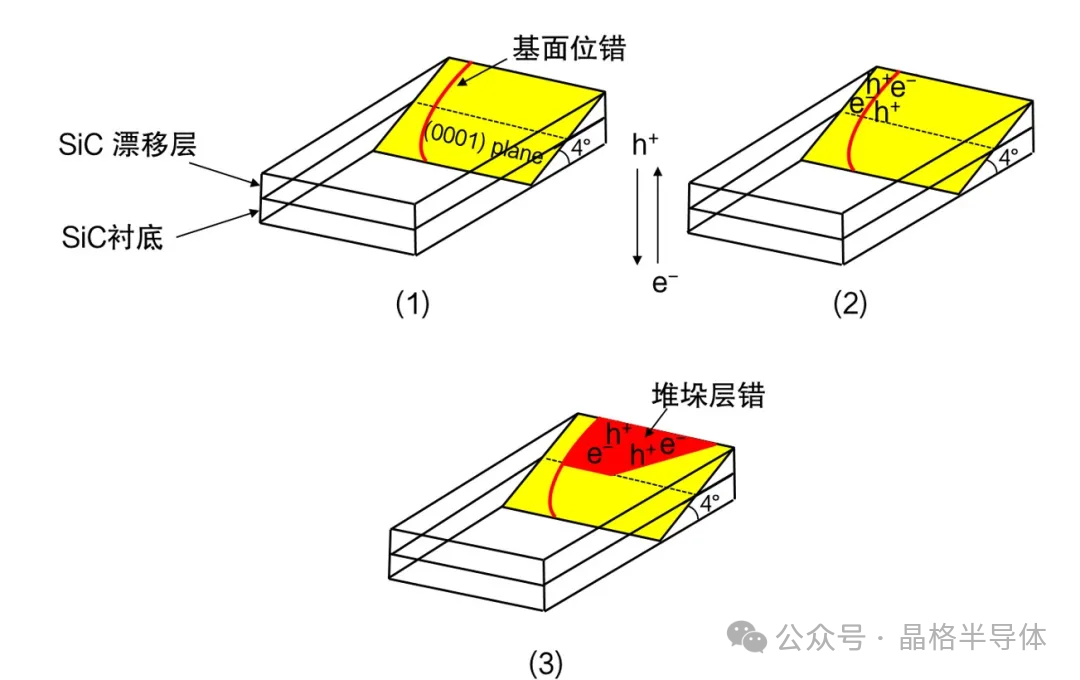

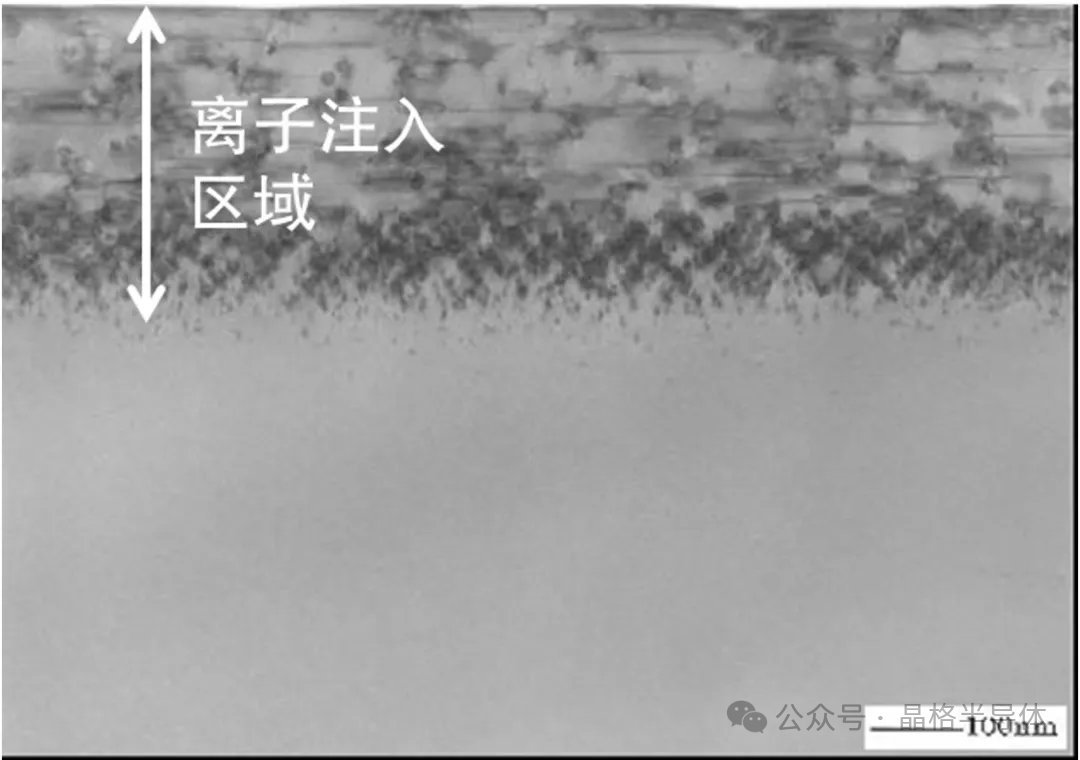

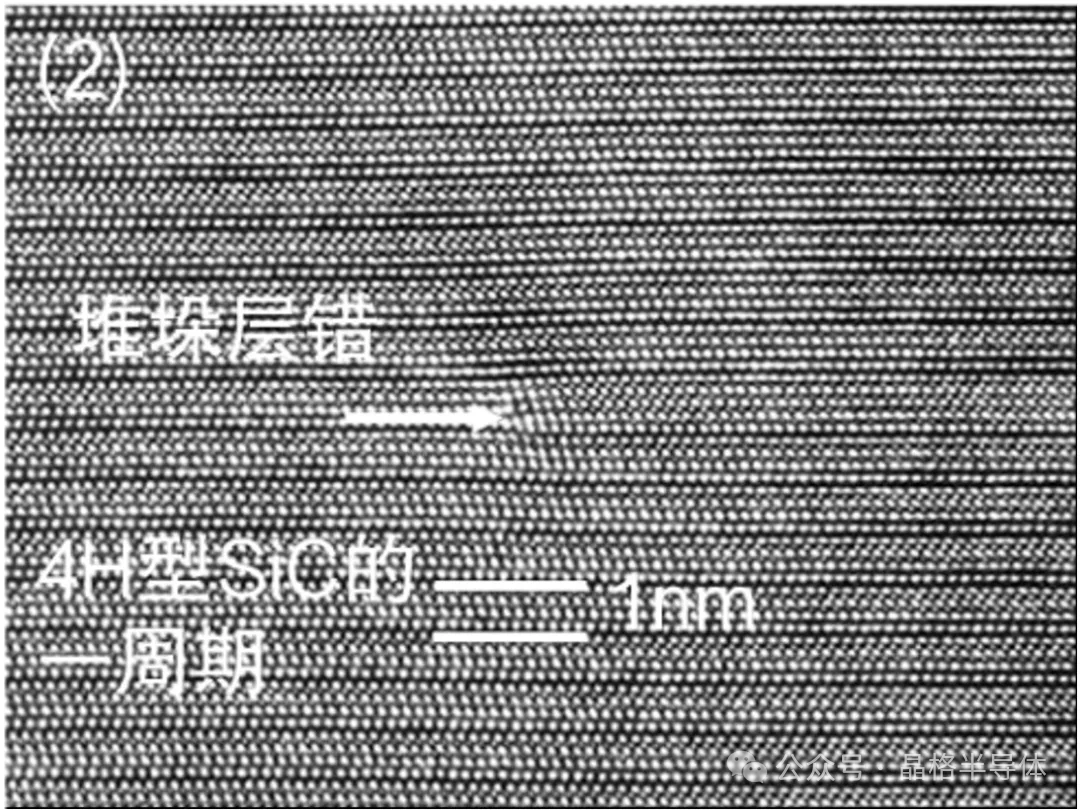

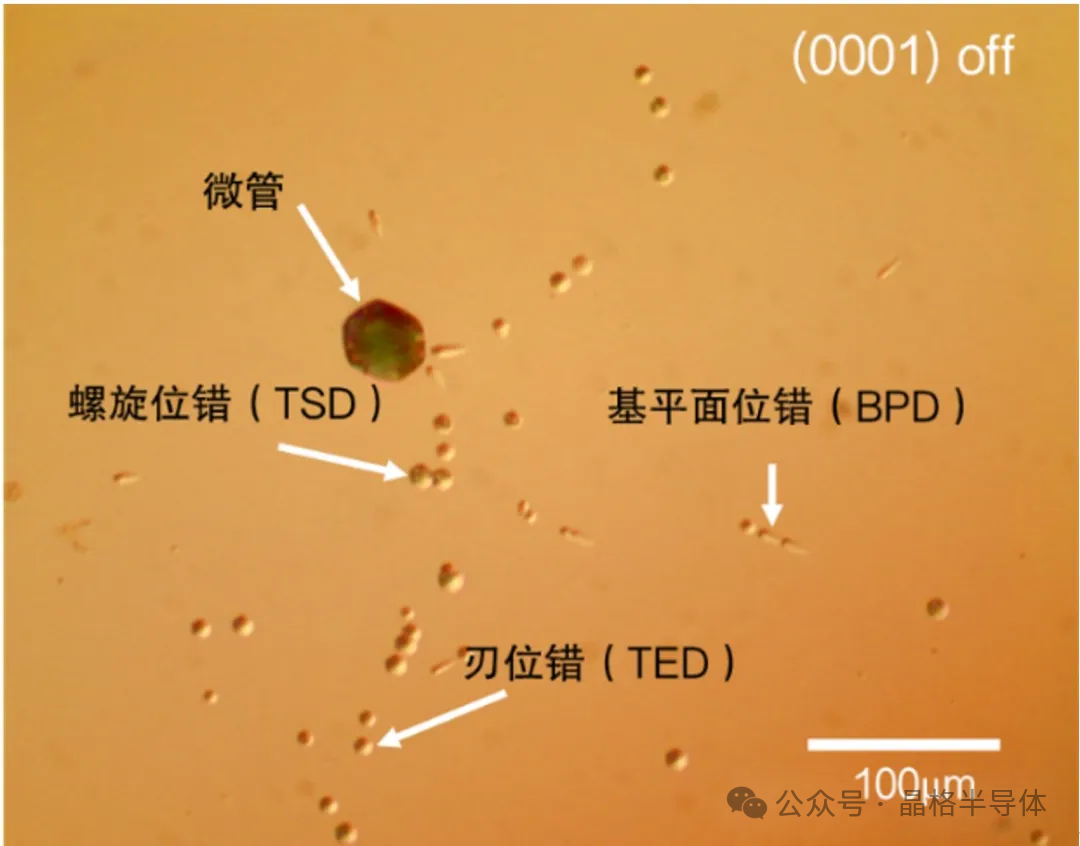

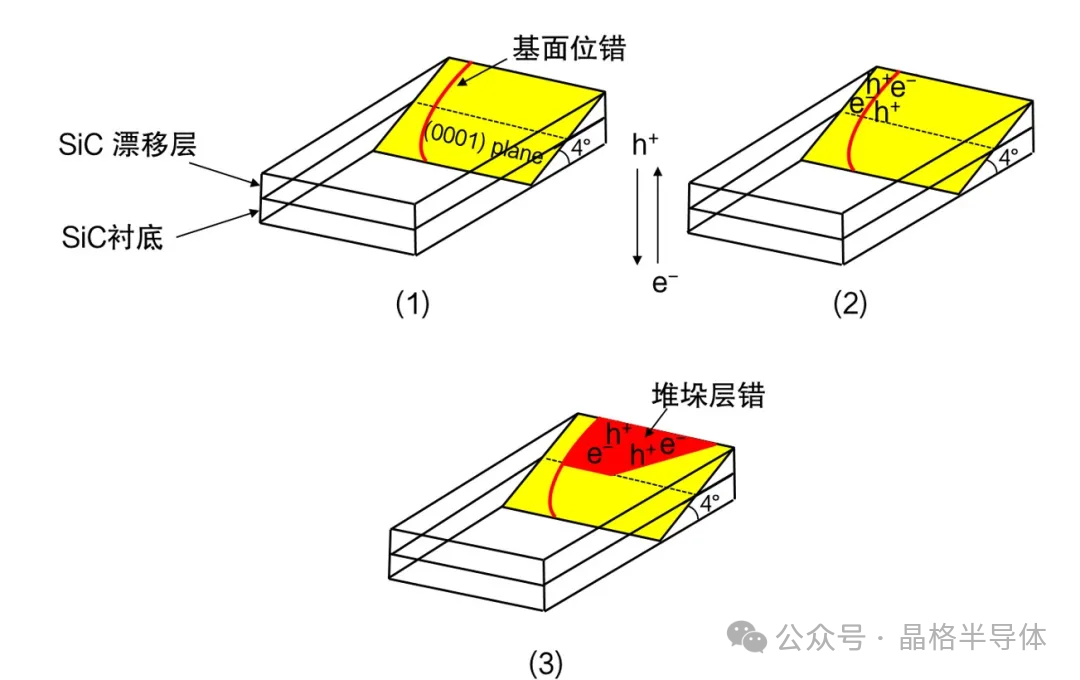

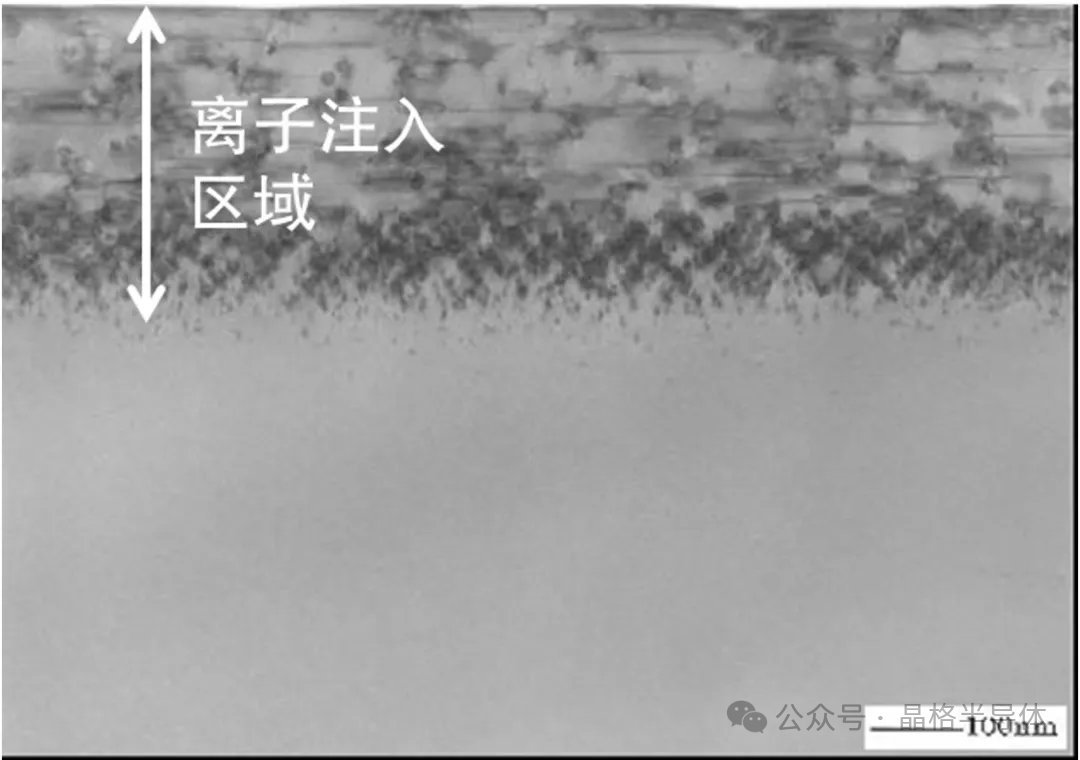

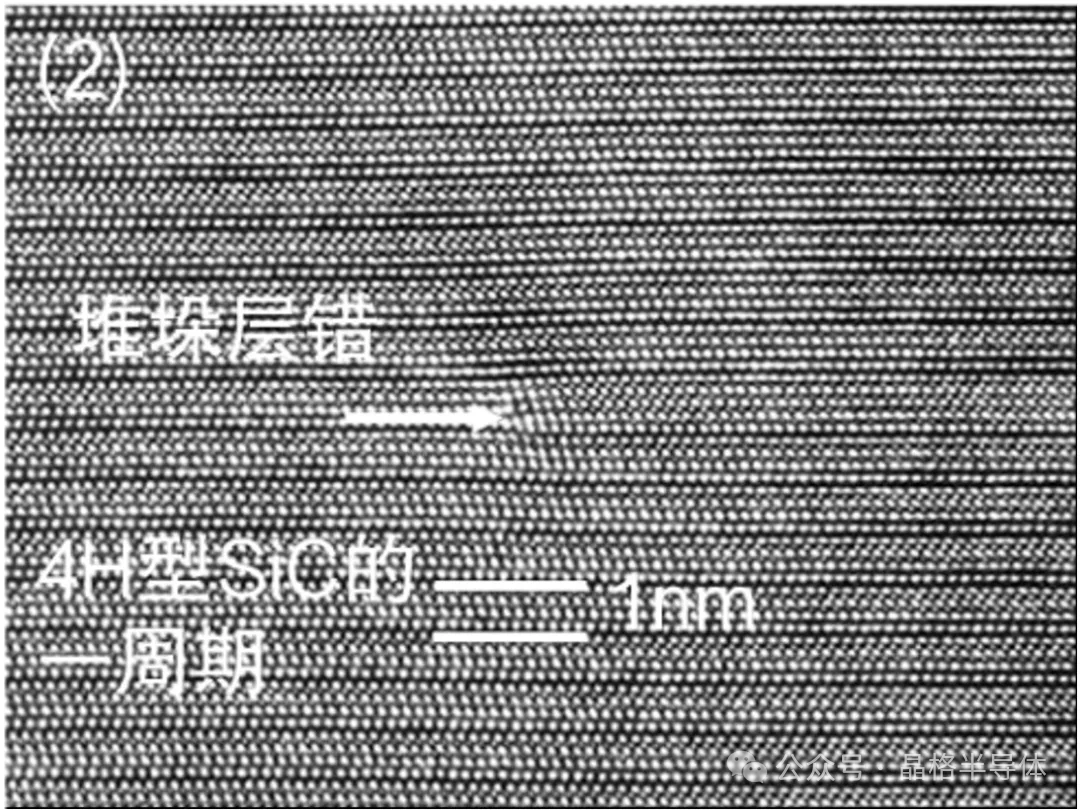

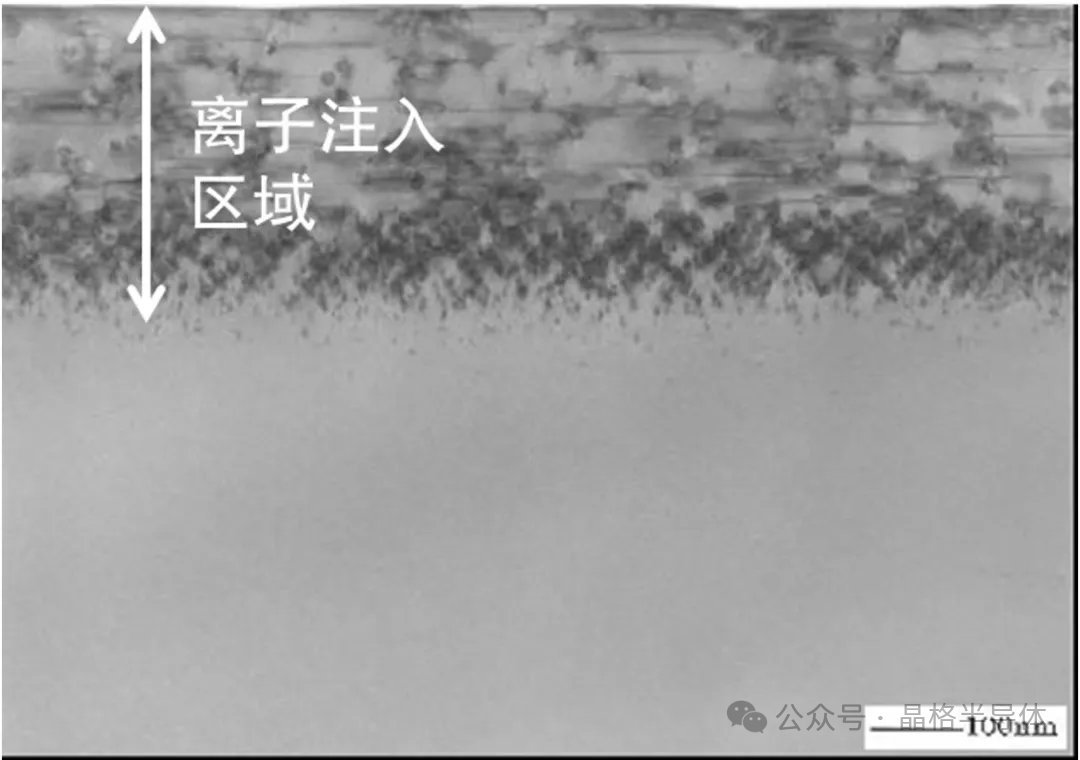

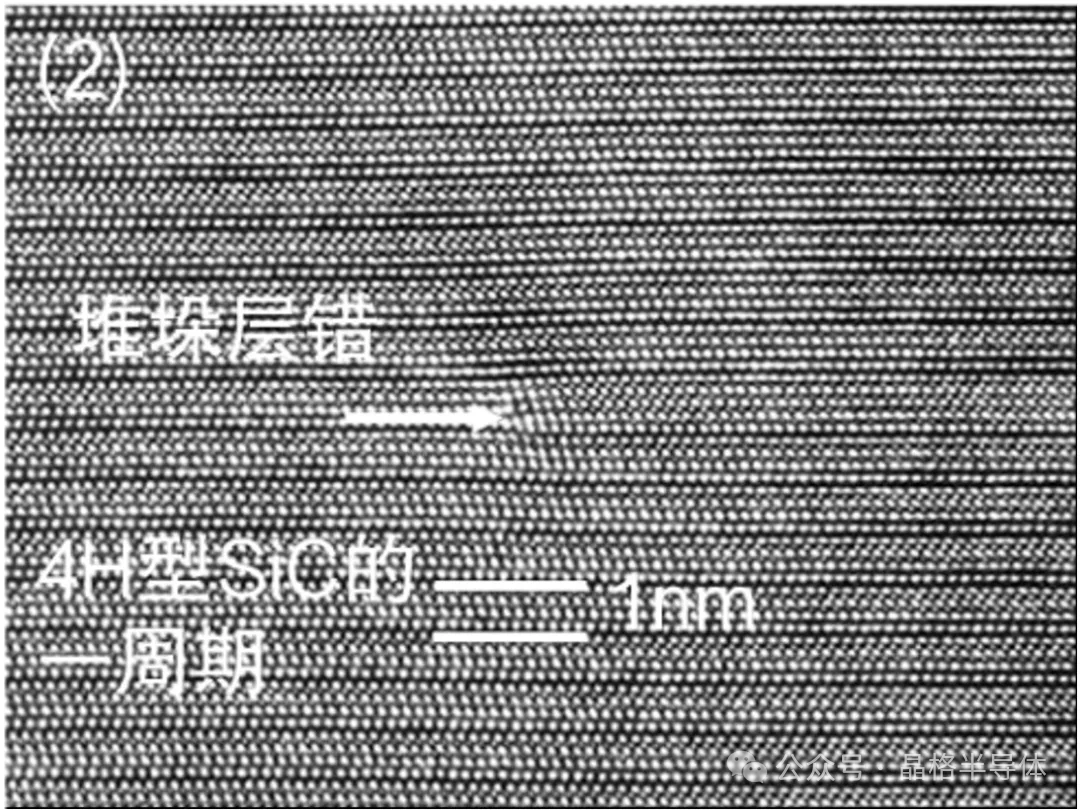

在 SiC 晶体之中,存在着各式各样的缺陷,而这些缺陷对 SiC 器件的性能有着直接的影响。所以,深入探究清楚各类缺陷的构成以及生长机制,显得尤为重要。接下来,就让我们一同去了解 SiC 晶体的缺陷情况,以及它们是怎样影响 SiC 器件特性的。SiC 晶体里的缺陷类型颇为丰富,主要涵盖了像微管、晶界、多型夹杂物、碳夹杂物这类大型缺陷,同时还有堆垛层错(SF)、刃位错(TED)、螺旋位错(TSD)、基面位错(BPD)以及由这些位错形成的复合体混合位错。就密度方面来看,在近期质量相对优良的 SiC 晶体中,微管的密度大概处于 1 至 10 个 /cm² 的范围,而位错的密度则约为 10³ 至 10⁴个 /cm²。直至如今,相较于 Si 来说,SiC 晶体的缺陷密度依旧是比较大的。微管其实可以看作是位移程度非常大的螺旋位错,其中心存在着空洞。至于碳夹杂物,它是在块状晶体生长的过程中嵌入进去的碳尘异物,还是产生高密度位错的源头,对于器件而言,这些都属于极为致命的缺陷。上图呈现的是利用熔融 KOH 对 8° 偏角(0001)4H-SiC 衬底的表面进行蚀刻后,在晶体缺陷部位形成凹坑的显微镜照片。我们可以看到,位错线朝着垂直于表面的方向延伸,这恰好反映出了晶体的对称性,经过蚀刻后便出现了六角形的凹坑。而基面位错处于(0001)面(也就是与表面平行的方向),其位错线朝着不同方向延伸,由此形成的凹坑呈现出椭圆形的形态。在螺旋位错中,存在着多个晶体偏移大小各异的位错。那些晶体偏移较大的螺旋位错以及混合位错,会使得器件中产生漏电流,不过对于小型位错而言,多数情况下并不会对器件性能造成影响。仔细剖析基面位错的结构,能够发现它呈现出一种被两个部分位错(即 Shockley 部分位错)所包围的线性结构。当双极性电流流经 SiC 器件时,在基面位错被两个部分位错包围的区域,会出现堆垛层错扩展的现象,这便是致使电阻增大等器件特性出现劣化的原因所在。上图对双极电流流过时堆垛层错的扩展过程做出了解释:首先,存在于 SiC 衬底中的基面位错会延伸到漂移层之中。其次,当双极性电流流过的时候,漂移层中的电子和空穴会被基面位错所俘获。然后,被俘获的电子和空穴会发生复合,并释放出能量。释放出的能量会促使部分位错移动,移动的部分进而形成堆垛层错,而堆垛层错区域又会进一步俘获电子和空穴,最终导致部分位错持续移动(也就是堆垛层错区域不断扩展)。形成堆垛层错的区域实际上起到了高电阻区域的作用。在高浓度 n 型区域,由于电子和空穴的复合寿命比较短,缓冲层或者衬底的空穴密度相对较低,所以堆垛层错的扩展往往发生在漂移层当中。并且,堆垛层错有着晶体学上稳定(也就是不会移动)的边界,因此,扩展后的堆垛层错区域大多呈现出典型的矩形或者三角形的形态。通过合理设置外延生长的条件,能够在很大程度上减少漂移层中的基面位错。当下,SiC 外延技术借助采用适当的缓冲层,已经可以显著降低漂移层中基面位错的密度了。在对 SiC 进行离子注入操作时,同样会产生晶体缺陷。图 3 和图 4 展示了对 SiC 进行高浓度 Al 离子注入后再经过退火处理的横截面 TEM(透射电子显微镜)图像。从图 3 中能够看出,在注入 Al 的区域存在着因变形而看上去呈现黑色的高密度缺陷,即便经过了高温退火处理,晶体也没能完全恢复到原有状态。在图 4 中,对缺陷部分进行了放大,展示出了高分辨率 TEM 图像(也就是晶格图像),从中可以观察到每 4 层构成一个周期(周期为 1 纳米)的结构,这表明此处为 4H-SiC。图中箭头所指的位置插入了一层多余的层,进而形成了 Frank 堆垛层错。就这一部分而言,已知注入的元素(比如 Al 等)会以层状的方式聚集在一起,最终形成堆垛层错。

离子注入所产生的缺陷被认为能够充当载流子的复合中心。例如,在 SiC 的 PN 二极管中,这种缺陷会使存储电荷减少,并且降低反向恢复电流。近来,也有相关尝试,试图将离子注入产生的缺陷作为抑制 SiC MOSFET 体二极管特性劣化的一种方法。