不同晶向的单晶硅维氏硬度有什么差异

时间:2025-07-16 发布人:admin 点击数:0

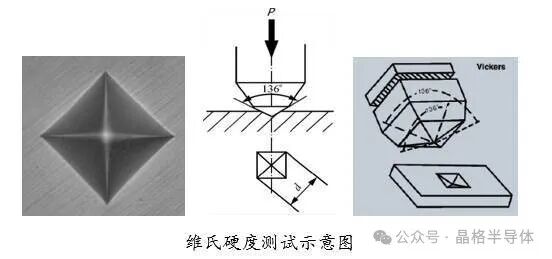

维氏硬度测试基于对角线压痕法:使用金刚石正四棱锥压头(夹角 136°),在选定载荷(如 0.1kgf~10kgf)下压入材料表面,通过测量压痕对角线长度计算硬度值(公式:HV=1.854F/d^2),其中F为载荷,d为对角线平均值)。相较于洛氏硬度、布氏硬度,维氏硬度的优势在于:

- 各向异性敏感性:压痕尺寸微小(微米级),可精准反映单晶硅不同晶向的硬度差异;

- 载荷适应性:可在极轻载荷下测试薄膜、表层等微小区域,适用于单晶硅片(厚度仅 0.5~1mm)的无损检测;

- 数据统一性:同一材料在不同载荷下的硬度值基本一致,避免了其他硬度测试的载荷依赖性问题。

单晶硅具有金刚石立方结构,原子按面心立方点阵排列,晶胞中每个硅原子通过共价键与 4 个邻近原子连接,形成高度对称的空间网络。这种结构决定了其力学性能的显著各向异性:

- <100> 晶向:原子排列呈正方形网格,晶面间距较大(0.543nm),维氏硬度约为11.5GPa;

- <110> 晶向:原子排列为矩形网格,晶面间距 0.392nm,硬度升至13.0GPa;

- <111> 晶向:原子呈密排三角形排列,晶面间距最小(0.314nm),硬度最高,可达13.5GPa。

这种差异源于不同晶向原子间结合力的方向性 —— 密排晶向(如 <111>)需要更高能量才能破坏共价键网络,从而表现出更强的抗形变能力。随着温度升高,单晶硅原子热振动加剧,共价键有效结合能下降,维氏硬度呈现非线性衰减。室温(25℃)下硬度约 12GPa,当温度升至 500℃时,硬度降至 8GPa 以下。这一特性对高温加工(如离子注入后的退火工艺)中的晶圆形变控制至关重要。当载荷小于 100gf 时,压痕深度进入亚微米级,表面层缺陷(如氧化层、加工损伤)对硬度值的影响显著增强。研究表明,10gf 载荷下测得的硬度比 100gf 载荷高约 5%,这是由于表层原子键合状态与体内存在差异。工业检测中通常采用 25gf~100gf 载荷,以平衡精度与表层干扰。切割损伤:线锯切割后的晶圆表面存在微裂纹和亚表面损伤层,硬度测试值可能比理想值低 10%~15%;抛光质量:化学机械抛光(CMP)后的原子级光滑表面(粗糙度 < 1nm)可消除表层缺陷,使硬度测量更接近理论值;氧化层影响:自然氧化层(约 2nm 厚 SiO₂)硬度(~8GPa)远低于单晶硅本体,需通过刻蚀去除后再测试。位错、空位等晶体缺陷会降低局部硬度,因为缺陷周围原子键合强度减弱;掺杂原子(如 P、B)对硬度的影响具有浓度依赖性:低浓度掺杂(<1e19cm⁻³)时硬度变化可忽略,高浓度掺杂(如重掺杂 Si:P)可能导致硬度微增(约 2%~3%)。由于 <111> 晶向硬度最高,切割 < 111 > 晶向晶圆时需采用更高硬度的金刚石线锯(粒径 50~70μm),并降低进给速度(比 < 100 > 晶向慢 20%)以减少裂纹;研磨过程中,利用硬度各向异性设计研磨压力 —— 对 <100> 晶向晶圆施加 1.5N/cm² 压力,而 < 111 > 晶向需增至 2.0N/cm² 以保证材料去除速率一致。单晶硅维氏硬度高(~12GPa),但断裂韧性低(仅 0.7MPa・m¹/²),属于典型的 “硬而脆” 材料。在 MEMS 器件加工(如深反应离子刻蚀 DRIE)中,需通过控制压痕应力(避免超过 1/10 硬度值,即 1.2GPa)来防止裂纹扩展。当在单晶硅表面沉积氮化硅(SiN,硬度~20GPa)、氧化硅(SiO₂,硬度~8GPa)等薄膜时,界面处的硬度梯度会影响薄膜附着力。通过维氏硬度梯度测试(间隔 1μm 压痕),可优化沉积工艺参数,使界面硬度过渡区控制在 50nm 以内。单晶硅的维氏硬度不仅是一个物理参数,更是贯穿半导体制造全流程的关键指标:从晶体生长时的晶向选择,到晶圆加工中的工艺参数优化,再到器件制备中的界面力学设计,硬度的精确调控直接决定了芯片的性能与可靠性。随着半导体产业向 1nm 制程迈进,对单晶硅力学性能的表征精度已从微米级压痕(传统维氏测试)发展到纳米级原位测量(如 SPM 技术),而硬度与晶体结构、缺陷、表面状态的内在联系,将持续成为材料科学与工程领域的研究热点。